# Field-Programmable Gate Array (FPGA)

EB941-80-04

**EB941**

# FPGA Solution

**Course notes**

# **Contents**

| CHAPTER 1: ABOUT THIS COURSE                       | 4   |

|----------------------------------------------------|-----|

| CHAPTER 2: ABOUT PLD TECHNOLOGY                    | 8   |

| CHAPTER 3: GETTING STARTED                         | 20  |

| CHAPTER 4: GETTING TO KNOW QUARTUS II INTRODUCTION | 26  |

| CHAPTER 5: ADVANCED QUARTUS II FEATURES            | 41  |

| CHAPTER 6: DESCRIPTOR LANGUAGES                    | 57  |

| CHAPTER 7: BEHAVIOURAL DESCRIPTIONS                | 64  |

| CHAPTER 8: COMBINATIONAL LOGIC USING HDL           | 70  |

| CHAPTER 9: COMBINATIONAL LOGIC ASSIGNMENT          | 95  |

| CHAPTER 10: SEQUENTIAL LOGIC                       | 98  |

| CHAPTER 11: ASSIGNMENT - MODULO-SIXTY COUNTER      | 143 |

## **Chapter 1: About this Course**

#### **Introduction to this package**

This CD ROM contains a complete guide to using Quartus and to developing designs in block diagram format, in VHDL and in Verilog.

Our intention is that, with just a basic understanding of digital electronics, you will be able to teach yourself to program FPGAs in block diagram mode or using a high-level descriptive language.

This assumes a basic understanding of combinational and sequential logic. Note that Quartus itself is primarily a design tool for CPLD/FPGA technology, and is not a great package for learning Digital Electronics.

To help you understand the transition between conventional digital logic simulation and design in VHDL and Verilog, the CD ROM includes a number of designs for the Proteus circuit simulator. These are given in the 'PROTEUS FILES' directory.

#### How to use this CD ROM

This is a self-study resource. Whilst a teacher may introduce each topic, the intention that students use this resource to teach themselves.

The remit is to enable you to:

- use Quartus II as a programming tool for FPGA technology

- design complex digital systems using block diagrams in the Quartus environment

- program using the VHDL language

- program using the Verilog language

In working through this course, use the left hand menu to work through the topics in the order they are presented.

The path the course follows is:

- setting up Quartus II

- using Quartus II for simple designs

- using advanced features of Quartus II

- introducing Very High Level Descriptive Languages (VHDL)

- introducing behavioural VHDL

- exploring combinational logic using VHDL

- exploring sequential logic using VHDL

We strongly recommend that you learn either Verilog or VHDL, even though it is possible to use block diagrams for most of this work.

#### **Example projects**

Within the course, there are a number of sample projects, using Block Diagram Files (bdf), Verilog and VHDL Code files etc.

By default, these are found in the Project Files sub folder "C:\Program Files\Matrix Multimedia\PLT\_Course\Project Files". They are installed both for minimum and full installations. As a result, you have access to copies of the files, both for working on and for modifying.

The original files are on the CD ROM in the Project Files folder, should you need to replace files, or access the originals.

#### **Network users**

Users on a network, or restricted users on a standalone computer, may not have full access to the default Project files location. In this case, it is recommended that a copy of the Project files folder is available for each user, in their "My Documents" folder.

#### What you need

To get started you will need the following:

- a computer with Windows XP, or later;

- an EB940 FPGA Solution;

- an internet connection;

You will also need access to a conventional circuit simulator such as Tina, Multisim, or Proteus. You will find Proteus files for many of the circuits on this CD ROM in the 'PROTEUS FILES' subdirectory.

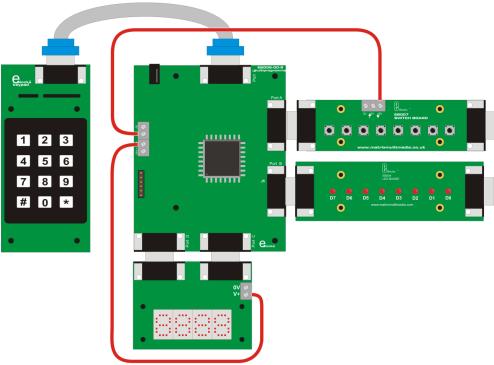

#### **FPGA** solution

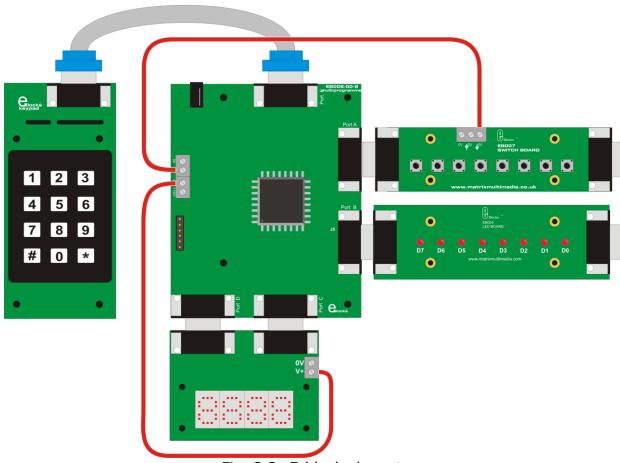

Fig 1.1: E-blocks FPGA Solution

Great for teaching modern digital system design

The EB940 FPGA Solution featured in this course includes a range of E-blocks and accessories:

- **E-Blocks** (with protective covers):

- o EB004 LED board

- o EB007 Switch board

- o EB008 Dual 7-segment display

- EB014 Keypad board

- o EB089 FPGA programmer / development board.

#### Accessories:

- o EB355 E-blocks User Guide

- o EB634 IDC cable

- HP2666 Power supply

- ELPLDSI Programmable Logic Techniques CD ROM + ELSAM mini CD ROM

Protective E-block covers and more...

#### **The importance of ALT - TAB and printing**

This course has been developed for use on-screen rather than in a document. The advantage of this approach is that it allows each topic and sub-topic to be presented to students in small manageable chunks - an approach that would result in a lot of waste paper in a conventional paper manual.

This approach also allows the use of hyperlinks to gain direct access to files, while the full course structure is visible at all times. When discussing program listings, this approach allows the program to be presented on one side of the screen whilst the text on the other side can be scrolled up and down. However some sections of the course are best printed out and followed on paper.

If you hold the ALT key down and press the TAB key at the same time, you toggle between the applications that are currently open on your computer desktop. This is useful when working through instructions in Quartus.

# **Chapter 2: About PLD technology**

#### **Introduction**

In this section you will learn about:

- the relationship between PLA's/ CPLDs / FPGA's;

- the main providers of PLA's/ CPLDs / FPGA's;

- the FPGA we use and its characteristics;

- the importance of PLA's/ CPLDs / FPGA's.

- The importance in the electronics industry, and hence in education, of programmable logic devices (PLDs) and other reconfigurable logic devices is not immediately apparent.

In most instances, a microcontroller could perform the tasks traditionally carried out by a PLD. However the advent of FPGA technology has brought a new dimension to this argument.

This document explains the architecture of programmable logic devices, how they have evolved, and why these devices will become more important over the next few years.

#### In the beginning...

PLDs (Programmable Logic Devices) stem from the original technology used to make Programmable Read Only Memories which was developed at the start of the computing boom. A variation of this technology led to the creation of Programmable Array Logic devices (PAL), which is where we start this discussion.

PAL s are simple logic blocks that provide a configurable combinational logic block. This does not seem that useful but when you consider that a single PAL might have replaced several TTL chips you can understand why their use was adopted all those years ago.

#### **PAL** architecture

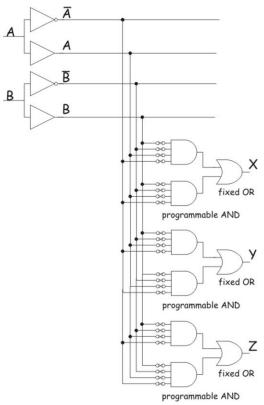

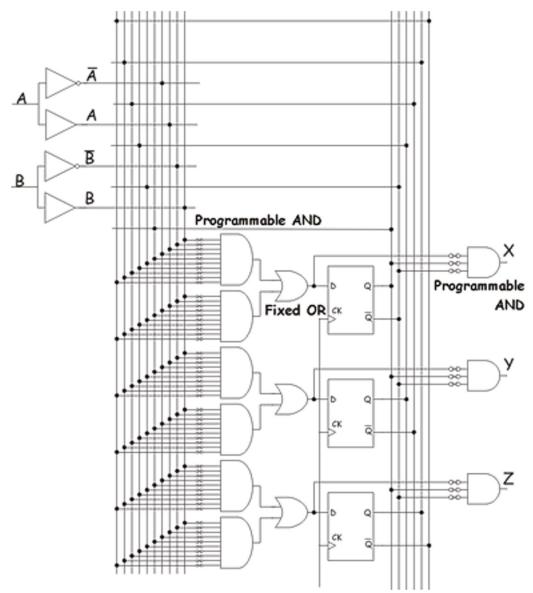

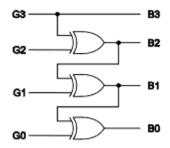

To understand how this works lets look at a simple diagram, shown below.

This represents the internal workings of a simple PAL with two inputs and 3 outputs. The terms A and B are inverted and buffered and made available to a series of AND gates with fusible inputs. The outputs are fed in turn to fixed OR gates and then to the appropriate outputs.

The mechanisms and constructions in silicon inside the device that allow this to take place are beyond this discussion. Here we are interested only in how the system works. This architecture, and a suitable system to lets us alter the state of the fuses, allows the outputs X, Y and Z to be any combinational logic variation of the two inputs A and B.

Fig 2.1: PAL architecture.

#### **PAL Example**

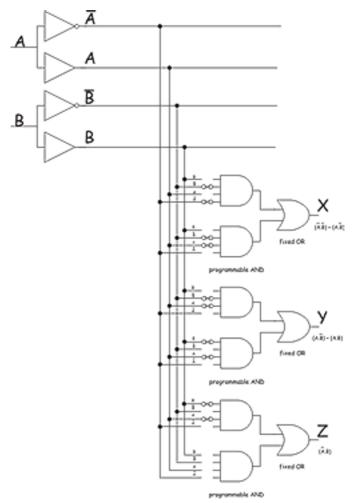

Assume we want the functions:

X = (A!.B!) + (A.B!)

Y = (A.B!) + (A.B)

Z = (A!.B)

(Here we use the '!' notation to denote inversion - it's just easier to type than a bar over the top of the letter.)

This new diagram would show you how the fuses would be orientated in the PAL. Note that the gate inputs float high when the fuse is blown.

Fig 2.2: PAL Example

#### **PALs and PLAs**

A Programmable Logic Array device differs slightly from a PAL in that both the AND terms and the OR terms are programmable. This results in a slightly more flexible device than a PAL but a device that is slightly more costly and complicated to program since more fuses need blowing. We won't look at the detail here!

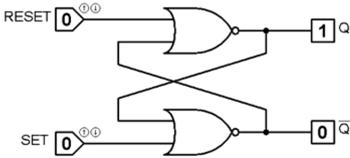

#### And so to PLDs

The addition of a single bit register in each output path allows the construction of state machines (in particular counters and shift registers). The resulting devices are very flexible and are generally referred to as Programmable Logic Devices or PLDs. The flexibility is greatly increased by feeding the outputs of the register bits back into the array itself allowing the construction of fairly complex designs.

To give increased flexibility, both the AND and OR sections of the circuit are programmable. The real circuits get rather complicated at this time but the following schematic shows the overall architecture.

Fig 2.3: PLD architecture

Here you can see that registers have been added to the 'fixed OR' gates and that their outputs are fed back into the central bus in the device. All the registers operate off the same clock signal.

The outputs can be selected from the OR gate or from the outputs of the D-type. In a real PLD, the combinational part of the device would be vastly more complicated (and flexible) than that shown here. Both the AND and the OR parts of the circuit would be programmable. You would also find that the outputs would be tri-state, controlled by further fuses, so that they can be declared as either an input or an output in the programming process.

From the diagram, you can see that a wide range of circuits can be built from such a device.

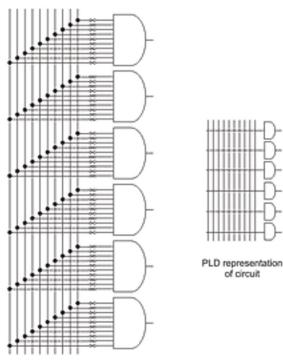

#### **Circuit representation**

As the architecture inside a PLD gets more complicated, it becomes increasingly difficult to draw a traditional circuit diagram of the device. Instead we use a schematic representation of the device, as in the diagram here:

Fig 2.4: PLD circuit representation

The inputs and fuses on the AND gates have been simplified to a single wire crossing each of the available lines inside the PLD. There are no junction 'dots' connecting the inputs to the available lines.

Designers understand that a connection can be made between any input and any available line by blowing appropriate fuses. This new representation allows 'schematics' for vastly more complex devices to be condensed to relatively simple diagrams.

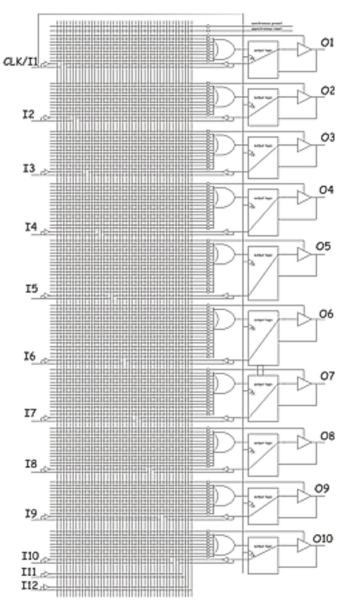

#### A real device

At this stage, we look at a real device. The 22V10 is a generic design, made by several manufacturers. It contains a large combinational logic block feeding 10 registers, or D-type flip-flops, whose outputs are fed back into the combinational logic block.

Fig 2.5: 22V10 chip

Showing the full circuit diagram in a conventional way gets very messy, and to understand its operation, we need to make some short cuts in how we draw the diagram. On the functional diagram, given below, the multiple input AND gates are shown by simply drawing a line across the appropriate logic lines and having a single input AND gate at the end of the line. Similarly the OR gate is shown spanning the eight inputs.

The actual circuit of each register block is slightly more complex than a simple D-type flipflop but this will do for our purposes.

Notice that the output from the flip-flop is shown on both the top right and also the bottom

left of the flip-flop.

Fig 2.6: A block schematic of a 22V10

The spare lines on the right hand side of the combinational logic block are used for synchronous reset and preset lines. You can assume that these are fed to all the output logic blocks. Notice that the number of AND lines on the OR gates vary from eight to sixteen.

#### **Packages and logic levels**

22V10s are available in a number of packages including DIL (24 pin,) PLCC and surface mount variations. They operate off 5V and are CMOS and TTL compatible.

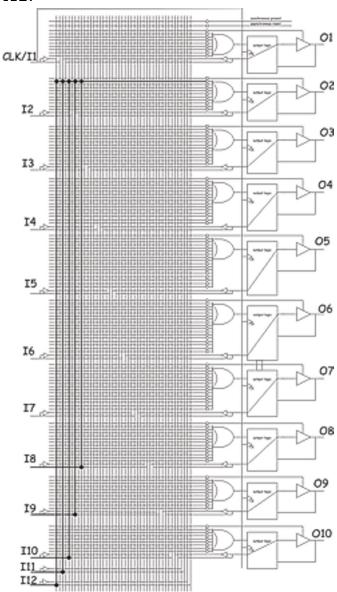

#### An example

To explain how this works, here is a representation of the fuses left intact (the dots,) and the input signal paths (the thick lines,) for a design where O2 will represent the ANDed inputs) I8, I9, I10, I11, I12:

Fig 2.7: 22V10 Example

#### **Exercise**

This exercise demonstrates how flexible the device is and helps to explain the structure of the device

Use the 22V10 diagram to develop an 8-bit counter that resets at a count of 10. You should print out a copy of the 22V10 - copy it from your browser and paste it into Word first - and mark with a dot the connections you want on the combinational logic lines, i.e. the fuses that are left intact after programming.

In formulating the answer to this task you may find the following table useful:

|     | 02 | 03 | 04 | 05 |

|-----|----|----|----|----|

| Z   | 0  | 0  | 0  | 0  |

| Z+1 | 1  | 0  | 0  | 0  |

| Z+2 | 0  | 1  | 0  | 0  |

| Z+3 | 1  | 1  | 0  | 0  |

| Z+4 | 0  | 0  | 1  | 0  |

| Z+5 | 1  | 0  | 1  | 0  |

| Z+6 | 0  | 1  | 1  | 0  |

| Z+7 | 1  | 1  | 1  | 0  |

| Z+8 | 0  | 0  | 0  | 1  |

| Z+9 | 1  | 0  | 0  | 1  |

Fig. 2.8

where:

Z is the state at the time of the first pulse;

Z+1 is the state at the time of the second pulse etc.

It will help to formulate the Boolean equations for each output state, before tackling the diagram.

For example: you can see that O2 is simply the inverse of its previous state.

This can be written as:

$$02(Z+1) = !02$$

This implies that all you need for the O2 line is an inverter between the O2 output and the flip flop feeding O2.

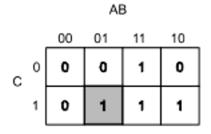

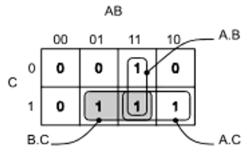

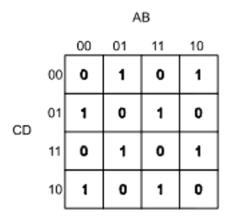

A Karnaugh map may help you to simplify the problem.

#### Why use a PLD?

A question that comes up often is: "Why should we use a PLD when a microcontroller is so easy to program and is so flexible?"

In the 1980's, when PLDs first came onto the market, the development path for microcontrollers was very inelegant. A microcontroller was a high volume, high commitment item with even 'One Time Programmable' devices not yet available. The use of PLDs was easy to justify then.

Today, reprogrammable microcontrollers are the preferred choice for many of the applications that PLDs used to perform. PLDs still have one great advantage over

microcontrollers - speed. Propagation times through a PLD are of the order of a few nanoseconds, which makes them about 100 times faster than the average microcontroller. As a result, PLDs are still useful in applications where timing is important, such as bus control and data multiplexing.

#### **Complex PLDs**

Even though devices like the 22V10 allow designers to mop up a large amount of 'glue' logic, in the form of 74xxx ICs, there are applications where more complex logic blocks are needed.

Hence Complex PLDs, (CPLDs,) were developed. These are basically a number of PLDs formed in a single package, with an even larger programmable interconnect block between the PLDs themselves. Combining PLDs in this way has advantages - reducing component count on the circuit board, increasing reliability and increasing the speed of the overall circuit.

These days CPLDs are available with up to over five hundred logic elements in packages of over two hundred pins.

As the complexity increases, we need yet another way of representing the architecture inside the CPLD, to help us to understand the device's structure and the functionality. We use a block approach.

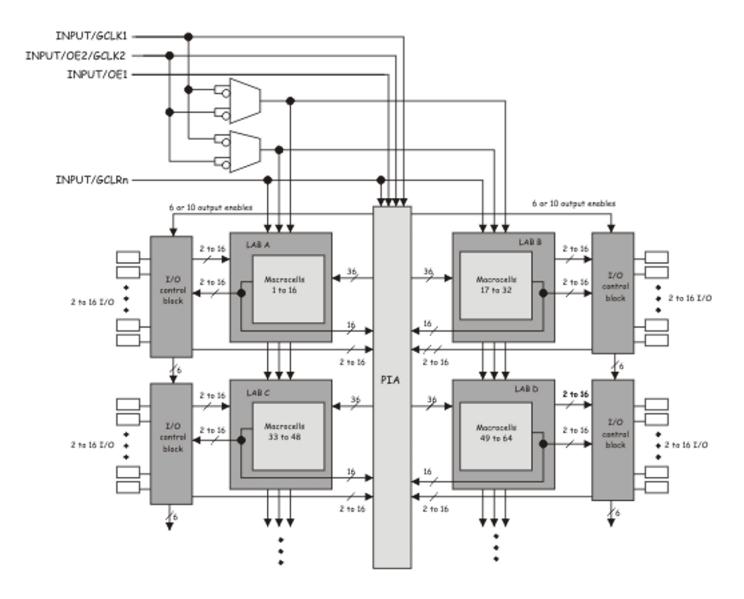

Look at the following diagram that represents the inner workings of an Altera 7000 CPLD device.

At the top of the diagram on the next page, you can see the various clocks and output enable lines which are multiplexed and fed to all the macrocells. The word 'macrocell' is used to refer to a programmable register logic block. You might also find this referred to as a 'logic element'. The macrocells themselves are bunched together in blocks of sixteen, each of which is associated with up to sixteen I/O (input / output) lines. The heart of the device is the PIA – Programmable Interconnect Array – which consists of a vast grid of signal lines that allows each macrocell to access all other lines in the device.

This basic structure is expandable. This allows manufacturers, like Altera, to make different versions of the device with different numbers of macrocells. As this number increases, so does the area of silicon required to implement it, and the size of the package which houses the device. The result is that the price increases as the number of macrocells increases.

At this point the actual internal architecture of the device becomes less important (unless you are going to design CPLDs). The design software, Quartus II, used to design and program these devices, shelters users from having to know too much about the architecture of the device.

Fig. 2.9: Complex PLD

#### **FPGAs**

Field Programmable Gate Arrays, (FPGAs,) take this architecture a step further. In addition to circuitry for simple state machine generation, each logic block within an FPGA also contains memory, which can be configured for a variety of topologies. We come back to look at the architecture of an FPGA later on, but here are a few key differences between FPGAs and CPLDs.

The most remarkable difference is the scale of the two devices. Whereas a CPLD contains a few hundred macrocells, an FPGA contains a few thousand. The Altera FPGA device shipped with the E-blocks development kit contains over 10,000 logic elements. FPGA's with millions of macrocells are available.

Even the most complicated of the designs in this course uses less than 1% of the resources of the FPGA.

Whilst the architecture of CPLDs and FPGAs is different, the software shields the user from these differences. The same software, Quartus II, is used for both CPLD and FPGA design. As far as a user is concerned, the difference between an FPGA and a CPLD is mainly that the FPGA is bigger. You can do more with it, but it costs more.

A key difference between CPLDs and FPGAs is that CPLDs are based on PROM-like technology, which allows the devices to retain their configuration when power is removed. On the other hand, FPGAs are based on Static RAM technology, which means that the contents need refreshing repeatedly. As a result, FPGAs need reprogramming each time the device is powered up, either directly from a PC, from a microcontroller or from static RAM.

One final difference between PLD technology and FPGA technology is that the FPGA operates at a lower voltage. Internally, the FPGA we use operates from a 1.5V supply which is buffered up to 3.3V for interfacing to the outside world.

#### Why use FPGAs?

Firstly, we need to restate that, in implementing a design, there is little difference between programming a CPLD and an FPGA. The software takes care of it all for you.

When looking at the question 'Why use CPLDs?' earlier on, the only real reason for preferring a CPLD to a microcontroller, was speed. As microcontrollers themselves are getting faster, that argument is weakening. However when asking the question 'Why use FPGA's?' the answer is very different.

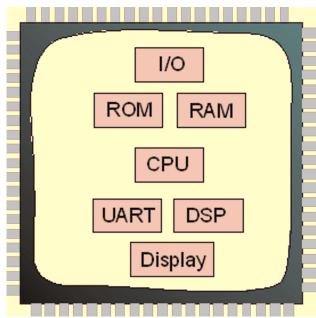

The argument will revolve around a new design methodology called 'System On Chip' or SOC. This refers to the capability to put an entire digital electronic system into an FPGA. For example, a designer can now implement an entire microcontroller, a digital signal processing system, a block of memory, a key pad interface, a graphical LCD display interface, and a USB interface on one single chip.

To do this, the designer uses software to define different parts of the FPGA to perform the relevant functions. The same software is used to link the design elements together. It can even implement a program in pseudo-ROM that the microcontroller can run.

The traditional method of implementing such a design in silicon would be to either link several integrated circuits together on a circuit board, or to develop an ASIC, (Application Specific Integrated Circuit).

The first solution, developing the system on a circuit board, would increase cost, decrease reliability, and increase design time. Developing an ASIC takes months and months, is extremely costly and is only therefore practical where large volumes are involved.

Fig. 2.10: FPGA system.

Using System On Chip designs has several advantages:

- · design cycles are short;

- the resulting system is totally reconfigurable;

- the design can be changed in production;

- it allows the same intellectual property to be reused many times.

A disadvantage is that it is still fairly costly, but as the technology matures, the costs are falling to a point where more and more ASIC designs are changing over to FPGA. Equally, with designs that previously used a microcontroller with a few support devices, these are now being replaced by FPGAs.

System On Chip is such an important technology that it alone justifies learning about this technology and how to program these devices.

#### Which FPGA?

Fig. 2.11: FPGA E-block EB089.

The FPGA device used is Altera's EP4CE10E22C8 FPGA which contains over ten thousand logic elements. The FPGA E-blocks board provides 5 full E-blocks ports to interface to other E-blocks boards, from simple LED and switch boards through to more complex boards like internet interfaces, IrDA communication systems, internet and Bluetooth boards.

## **Chapter 3: Getting started**

#### **Introduction**

Quartus II Web Edition design software is available from the Altera web site – www.Altera.com .

Altera make this function-limited version of Quartus available free of charge, but also allow educational institutions to upgrade to a fully working version of Quartus for a very reasonable fee.

For this course, the free version, Quartus II Web Edition, is more than sufficient. Please note that you may want to print out the next section and work through it whilst installing Quartus II.

#### Installation

The first task is to download the latest version of the Quartus II software from the Altera website. Currently, that is the Quartus II Web Edition v13.0 SP1.

The Altera web site is large so we will give guidance to finding your way around it.

- 1. Go to the Altera website, <u>www.altera.com</u>.

- 3. Click on the 'Free Web Package' button.

- 4. To be able to download the software, you have to create a 'myAltera' account, useful for on-line course registration later, follow the on-screen instructions.

- 5. Open and save the 'Quick Start Guide'.

- 6. You next need to specify:

- the operating system,

- preferred download method,

- software components.

You should include the ModelSim-Altera edition simulation software, and Cyclone II, III and IV device support. It is a good idea to download the Quartus II Help file as well.

- 7. Click on the 'Download Selected Files' button.

- It will take a while to download the 150MB or so zip file!

- 8. Extract all the files to the same directory.

- 9. Run the Quartus set-up program to begin the installation process, and follow the onscreen instructions.

#### **Drivers and cables**

The instructions in the previous section should enable you to get Quartus working.

The next step in the installation is to add the hardware. This makes use of software inside Quartus that allows programming via the computer's USB port, and uses the 'USB Blaster' device.

Fig 3.1: USB Blaster.

#### IMPORTANT -

Some operating systems may require a driver to enable Quartus to use the ''USB Blaster'.

In this case, the 'Found New Hardware' wizard opens and prompts you to install a new hardware driver.

Appropriate drivers are available from the Altera website.

Go to <a href="https://www.altera.com/support/software/drivers">www.altera.com/support/software/drivers</a> and download the appropriate driver to C:\altera\13.0sp1\quartus\drivers folder (or equivalent.)

Install the driver from this location.

(Further details are available in the 'USB-Blaster Download Cable User Guide', available from the Altera website.)

#### Setting up your hardware

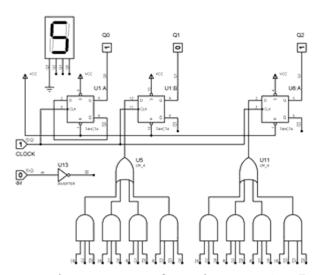

The basic set up of E-blocks for all tutorials in this course is shown in the diagram:

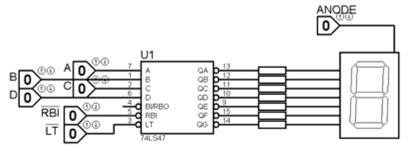

- the 7-segment display is on Ports C and D;

- the switch board is on Port A;

- the LED board is on Port B;

- the keypad to port E via ADC cable.

Fig. 3.2: E-blocks layout.

Take care to connect each E-blocks correctly, and to route power to the switch board and 7-segment display board (the red wires in the diagram).

#### Pin connections for hardware

With the E-blocks set up in the format described on the previous section, the pin connections are as follows:

#### Switch board:

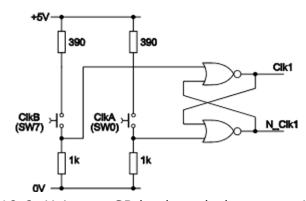

| Switch | Port A pin | FPGA pin |

|--------|------------|----------|

| SW7    | 8          | 120      |

| SW6    | 7          | 119      |

| SW5    | 6          | 115      |

| SW4    | 5          | 114      |

| SW3    | 4          | 113      |

| SW2    | 3          | 112      |

| SW1    | 2          | 111      |

| SW0    | 1          | 110      |

Fig. 3.3

#### LED board:

| LED | Port B pin | FPGA pin |

|-----|------------|----------|

| D7  | 8          | 84       |

| D6  | 7          | 83       |

| D5  | 6          | 80       |

| D4  | 5          | 77       |

| D3  | 4          | 76       |

| D2  | 3          | 75       |

| D1  | 2          | 74       |

| D0  | 1          | 73       |

Fig. 3.4

#### 7-segment display:

|                 |            | _        | • •     |            |          |

|-----------------|------------|----------|---------|------------|----------|

| Anode for char. | Port C pin | FPGA pin | segment | Port D pin | FPGA pin |

| 0               | 1          | 25       | a       | 1          | 15       |

| 1               | 2          | 27       | b       | 2          | 16       |

| 2               | 3          | 28       | С       | 3          | 17       |

| 3               | 4          | 29       | d       | 4          | 18       |

|                 |            |          | е       | 5          | 20       |

|                 |            |          | f       | 6          | 21       |

|                 |            |          | g       | 7          | 22       |

|                 |            |          | dp      | 8          | 24       |

Fig. 3.5

You may want to print this page out to refer to when you are developing your designs.

#### **Getting your hardware working**

In this section, you use Quartus to check that your hardware is working. Don't worry too much about understanding the design itself – you are concentrating on transferring the program.

Under the directory quartus project files on the CD ROM you will find a directory called simpleand.

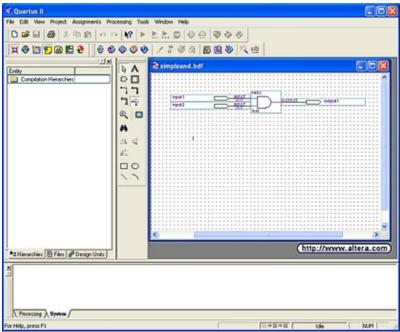

Open this folder and locate a file called simpleand.qpf. Open this file - you will see a screen like this:

Fig. 3.7: Quartus IDE.

This project is a simple AND gate. Its purpose is to ensure that you become familiar with the Quartus software.

This design has already been compiled and is ready to be sent to the FPGA.

#### **Configuring the programmer**

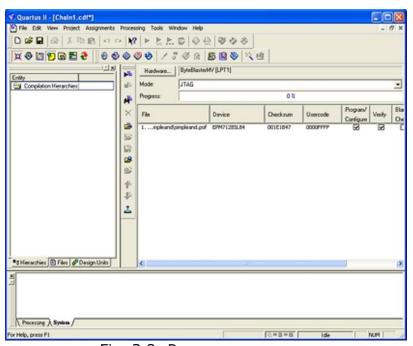

From within Quartus, select TOOLS...PROGRAMMER You should see a screen that looks like:

Fig. 3.8: Programmer screen

Firstly, select the type of hardware you have. For the board we provide, you will be using a USB cable, the USB Blaster.

To select this:

- click on the HARDWARE button;

- click ADD HARDWARE;

- from the HARDWARE TYPE drop down box, select USB Blaster;

- check 'USB Blaster' from the list of available hardware items;

- your 'Currently selected hardware' should be 'USB Blaster'.

Next select the programming technique:

• from the drop down box titled MODE, select JTAG.

If you have problems getting the programmer to work, make sure you have installed the latest programming drivers for your operating system.

#### **Programming the FPGA**

To the left of the programmer screen are a number of icons that control the programmer. If your file is not listed in the programmer screen, you need to select the file you want to program, and the program settings.

To do this:

- click on the OPEN icon;

- navigate to the original simpleand directory, and select the file simpleand.pof;

- click the check boxes under PROGRAM and VERIFY.

You are now ready to program your device.

To start, click on the START PROGRAMMING icon

**Hint** – if you are not sure of the function of an icon, hold your mouse cursor over it. A small pop-up hint appears, displaying the icon's function.

Once you press the button, the program is sent to the FPGA.

You can now test the AND gate. Pressing both switches SW0 and SW1 illuminates LED D0. This is a two input AND gate.

## **Chapter 4: Getting to know Quartus II Introduction**

Whether you are instructor or student, you need to respect Quartus. Quartus is a phenomenal design tool, used extensively in industry, very capable and very flexible. Its power and flexibility mean that it can also be quite complex to use for the novice,. Whilst it has learning potential for digital electronics, it is not perfect for all the phases of learning. This is particularly true for basic digital electronics, where students will struggle if they have to learn electronics and how to use Quartus, both at the same time.

We recommend that you use Quartus only when you have got a grasp of digital electronics.

#### **How to learn Quartus**

When looking at the materials supplied with Quartus, we found a number of problems for novices:

- the documentation supplied is very complex;

- the examples supplied are very complex;

- the assumed knowledge is high.

As a result, learning Quartus takes time and risks being frustrating.

For these reasons, we have provided some simple step-by-step projects that you can use yourself. These start at a very simple level and work up to much more complex designs, equivalent to many logic chips.

We recommend that you review the Quartus tutorial and documentation at a later stage. The examples may be complex but the manuals do give a very good picture of the design flow and the hierarchy within Quartus. The Quartus II Handbook and other support materials are available from the Altera website (www.altera.com).

#### A note on Wizards

The instructions for entering information in wizards should be used with care. When guiding you through wizards, we indicate only the main selections to make – please leave other items unchanged.

#### **Using this document**

This document contains instructions for designing a project from scratch. We have included quite detailed instructions so that you can follow the design flow. You can go through this document step-by-step and enter the design now, or you can skim through and try the exercises at the end coming back to this document when/if you get problems.

#### **Document conventions**

Within this document we will use the following conventions:

Courier will be used for anything that must be typed as it appears, such as a file name: C:\quartus\bin\quartus.exe

CAPITALS will be used for menu commands which you need to click on such as FILE..NEW Note: Quartus does not allow spaces in file names. For this reason we use underscores in file names throughout these tutorials.

#### **Design flow**

Before getting into your first design, it is worth considering all of the elements in it and in the Quartus package. You need to be aware of the different types of files you will create in producing the design.

The design flow stages within Quartus can be simplified to:

- design your circuit;

- compile your design;

- design your simulation;

- simulate your design;

- program your PLD.

This is vastly simplified. The Quartus documentation gives a more exhaustive list, but this will do for now. It goes without saying that this is not a simple linear process – you may find problems with your design, and need to revisit certain stages as a result.

In using Quartus, it may seem that there are a large number of steps in making even the simplest design. Understanding the top level design will give more meaning to the individual steps in the design process.

Each step results in the creation of two types of file - those you create as part of the design, and those Quartus creates containing results of the compilation and simulation processes.

At the top of the hierarchy is the Quartus project - a set of files that stores information about your design. Within that, the main files are the Quartus Project file (file extension `.qpf') and the Quartus Settings File (`.qsf').

You will find that there are a large number of other files created – a simple traffic light project results in around 37 different files in the design directory and about 20 files in the db subdirectory, most of which you never need to worry about. This can look a little daunting but is a result of the very modular approach Quartus takes to design flow, which increases its flexibility.

#### Files you will create

The processes in the design flow outlined above create a large number of files, with a variety of file extensions. It is more important to appreciate that these divide into two main types - simulation files and design files - than to know the specifics of each file.

When designing projects using a conventional block diagram approach, you create \*.bdf files: **b**lock **d**iagram **f**iles. These contain the core of your design. You may end up with several of these in one design – Quartus allows you a hierarchy of these to simplify the design process.

Each design you produce should be simulated to verify that the design does what it is supposed to. Initially, this simulation does not take place in 'real time', and so cannot be used to test the effects of the design on LEDs and 7-segment displays and other hardware.

This course does not cover simulation. There is a wide variety of tutorial material on simulation on the internet.

It is important to understand that when using Quartus, you are working with projects - collections of files. You never really work with individual files as you might do with other design tools.

#### **The Quartus GUI**

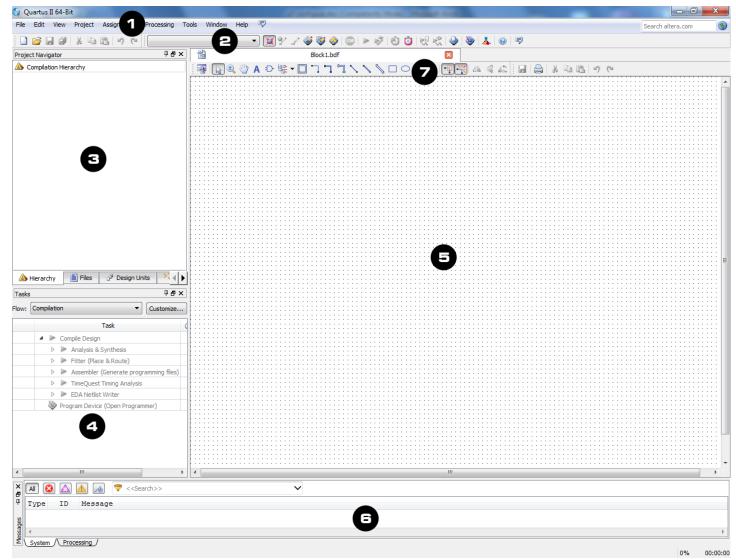

Before you start, you need to identify parts of the Quartus design environment. When you first load Quartus and select FILE....NEW BLOCK DIAGRAM FILE, your screen will resemble this (depending on the version of Quartus used, and the way it is set up):

Fig. 4.2: Quartus GUI

The areas numbered in this image are:

- 1. a standard Windows tool bar, giving access to all functions within Quartus;

- 2. two icon fields, which give quick access to major functions within Quartus; (All of these are also accessible via menus. Throughout the course, we refer to the menu commands rather than to the icons.)

- 3. the Project Navigator, which allows you to see the hierarchy of your project and the files it contains;

- 4. the Status window, showing the status of various operations (such as simulation and compilation);

- the design area, where you actually enter the design information;

- 6. the Message window, where Quartus displays error and warning messages during

simulation and compilation tasks;

7. the Block and Symbol Editor toolbar.

With the exception of item 7 you can make these items visible and invisible by selecting VIEW....UITILITY WINDOWS.

#### **Introduction to design**

In creating a new design from scratch, you need to:

- 1. run Quartus and choose toolbar options, etc.;

- 2. create a Project;

- 3. choose your preferred method of design entry: schematic, HDL, etc.;

- 4. enter a basic design using schematic, Verilog and VHDL;

- 5. choose and use appropriate compiler options;

- choose and use appropriate simulator options;

- 7. download your design to the Matrix Multimedia FPGA board;

- 8. test your design.

Next, you will work through all of the points mentioned above, except simulation.

The steps that follow use the same numbering to help you keep track. You may wish to print out each section as you go through it.

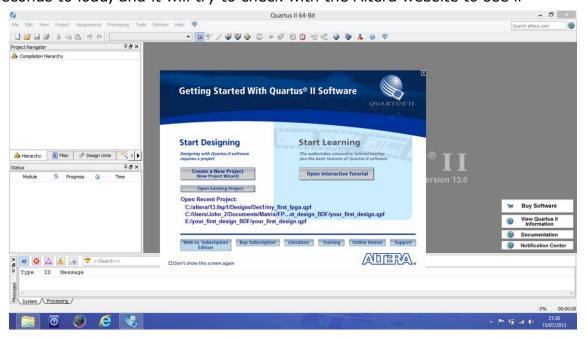

#### Step 1: Run the Quartus software.

The default installation requires you to run Quartus by clicking START\PROGRAMS\ALTERA\13.0SP1\QUARTUS\QUARTUS II 13.0SP1 WEB EDITION, (or similar). Alternatively, there may be an icon on the desktop. The quartus.exe file itself is found in a location such as  $C:\altera\13.0sp1\quartus\bin64$  folder (amongst several thousand others!).

It may take several seconds to load, and it will try to check with the Altera website to see if

there are any updates, so be patient!

Once it has loaded your screen should

look something like

the image below.

Fig. 4.11: Quartus opening screen.

The large (main) window is used for working on design files. The two smaller windows on the left are the Project Navigator (top) and Status windows. You can choose whether these are displayed using the View/Utility Windows menu.

The Toolbars can be customized so that only a few of the many command buttons are displayed. Your personal preferences may not agree with these settings, but these notes assume that you can click the buttons listed below. You can also access all the facilities via the main menus, and such menu routes will be given.

In order to reproduce the arrangement shown, use the TOOLS/CUSTOMIZE... facility. Turn off all the toolbars apart from Standard Quartus II then use the Commands tab to drag the following command buttons onto that toolbar, from the given 'Actions':

Applications - Programmer

Assignments - Settings, Pin Planner, Assignment Editor

Compiler - Start Analysis and Synthesis, Start Analysis and Elaboration, Start Compilation

Edit - Undo

File - New, New Project Wizard, Save All

Help - Search

Project - Set as Top-Level Entity

To remove any unwanted command buttons, simply drag them off the toolbar. Then click OK (twice).

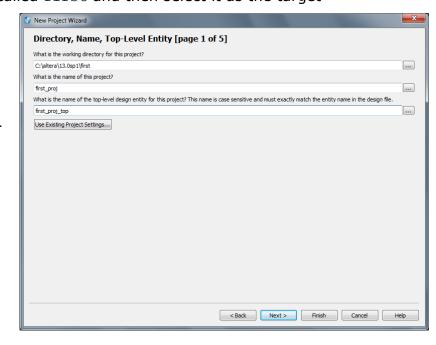

#### Step 2: Create a New Project

Click the New Project Wizard button [4] (FILE/NEW PROJECT WIZARD) and take a quick look at the information on the first page that opens. Then click NEXT.

You need to specify the location and name of your project, and the folder (directory) containing it. The target directory will be set to the C:/altera/13.0sp1 folder by default. However, for this project, create a folder called first and then select it as the target

directory (C:/altera/13.0sp1/first). You can create it somewhere else if you wish, for example,

C:/altera/13.0sp1/quartus/qdesigns folder is one alternative, just make you know where the folder (directory) is!

You also have to think up a name for your project, and a name for the 'top entity' in it. Use the suggestions given in the image below.

(C:\altera\13.0sp1\first,

first proj, first proj top)

Fig. 4.12: Page 1 of New Project Wizard.

When you click NEXT, Quartus asks if you

wish to create the first folder for your project, if it does not already exist Click on Yes', and page 2 of 5 of the Wizard opens.

There are no design files to add to your project, so click Next to get to page 3.

On page 3, you select the family of the specific device you wish to use. The chip on the Matrix Multimedia FPGA board is a member of the Cyclone IV E family, so select that option in 'Device family'. In the 'Target device' section, click on 'Specific device selected in 'Available devices' list'. Scroll down the 'Available devices' list and click on the 'EP4CE10E22C8' device used on the Matrix Multimedia FPGA board. Then click NEXT.

You are not going to use any EDA (Engineering Design Automation) tools apart from Quartus itself, so leave all the options to 'None' and click NEXT.

Page 5 confirms your choices. Check that you have selected the EP4CE10E22C8 device and that the other files and folders are correct. Click BACK if you need to change anything, otherwise click FINISH.

What exactly have you created? Use Windows Explorer to verify the following.

- The first folder has been created in the C:/altera/13.0sp1 folder.

- Inside that, there is a Quartus Project File (.qpf) and a Quartus Settings File (.qsf) in the first folder.

- There is a db folder within the first folder.

- There are two files inside that folder.

If you were to close Quartus now, the next time you run the program, your project could be called back by clicking FILE > RECENT PROJECTS > C:/altera/13.0sp1/first proj.qpf.

#### Step 3: choosing your design entry method

In this first exercise, you are going to create a new design, using the schematic drawing entry method. (Later you will learn about Verilog and VHDL design entry methods.)

Click the New button or select FILE/NEW... and BLOCK DIAGRAM/SCHEMATIC FILE option and click OK. A new file opens in the main window together with the Block and Symbol Editors toolbar. The Quartus software names the new file Block1.bdf.

#### Step 4: enter your design

You are about to create a design comprising just one AND gate!

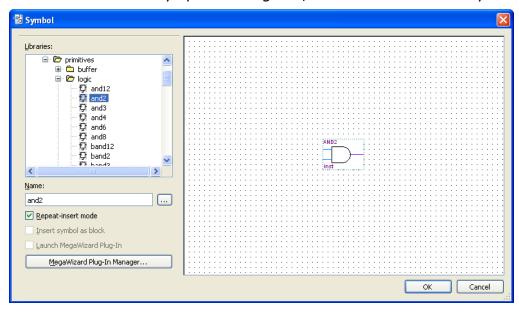

Click the (Symbol Tool) button in the Block and Symbol Editors toolbar. The Symbol dialogue window allows you to select different symbols. Click on the folder or the symbol next to it to open the 'libraries' folder, then open the 'primitives' folder. Inside that, open the 'logic' folder. Select the 'and2' device, and click OK.

Click once in the schematic file drawing area to place one instance of a 2-input AND gate.

Click the button ('Selection Tool') or press the 'Esc' key to release the AND gate from your mouse. Select and delete any spare AND gates, that were inadvertently created.

Fig. 4.13: Schematic symbol selector.

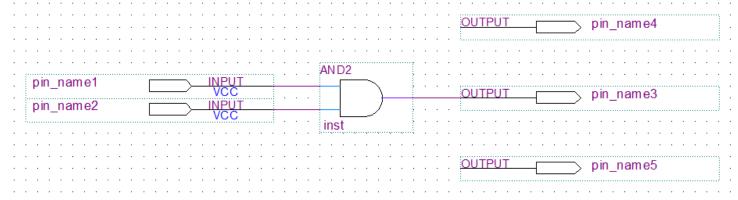

As well as the AND gate, your design requires input and output 'pins'. These allow you to specify physical characteristics of the design, such as the pin numbers of the chip to use. Use the Symbol Tool again but this time select the 'libraries/primitives/pins' folder. Select the input pin device, and click OK. Place an input pin to the left of each input connection of the AND gate.

Next, in the same way, select an output pin device from the 'libraries/primitives/pins' folder. Place one to the right of the AND gate output connection, and add two more as shown below.

Fig. 4.14: AND gate design.

Now you can wire up the two input pins, and the three output pins. To do so, you click on one connection point, hold the mouse button down, drag the wire to the other and then

release the mouse button. Wires are laid out automatically with just vertical or horizontal runs ('orthogonally').

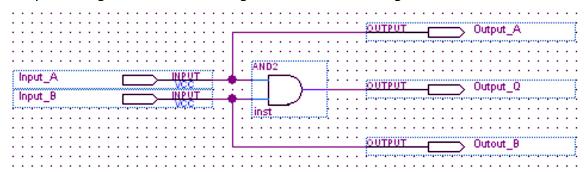

You can click on the Orthogonal Node Tool ( ) or just hover carefully over the component connection point to get into wiredrawing mode. Your drawing should start to look like:

Fig. 4.15: Partially completed AND gate design.

Edit the names of the input and output pins by double-clicking them. Use the names given in the diagram.

Now select FILE > SAVE AS... A dialogue box should open, expecting you to name the file first\_proj\_top.bdf, since this was the information given in the New Project Wizard, and to save it in the first folder. If these are the settings in the dialogue, go ahead and click SAVE, otherwise enter the required file and folder names and then save the file.

#### Step 5: set the compiler options and analyse the design.

At this stage, your design needs to be analyzed. This checks for errors, but also allows the software to recognize the input and output names you entered on the schematic.

This forms part of the compiling process, but before you run the compiler you need to check that the system will analyse the right things for you. Even though, in this, your first design, there is only one file, you still need to make sure that Quartus looks at it in the right way!

Click the Settings ( ) button (or click the ASSIGNMENTS/SETTINGS... menu). The Settings - first proj top dialogue opens.

Click the GENERAL option in the 'Category:' list and ensure that the top-level entity is first proj top.

Next, check that the 'Files' category contains just the first\_proj\_top.bdf Block Diagram/Schematic type file. Now click OK.

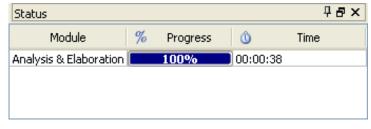

Click the 'Start Analysis and Elaboration' button via the PROCESSING/START/ menu (Processing > Start > Start Analysis and Elaboration).

After a few seconds activity, the Status window should show the following:

Fig. 4.16: Analysis and Elaboration.

If there are any problems with your design, the compiler will stop sooner, and some error messages will appear in the Message Window below the Main Window in the Quartus screen. Attend to the messages and re-analyse.

If you take a look at the files in your first and first/db folders, you should find that there are now almost fifty files. (You may need to refresh the Explorer window in order to see all the new files, if you have had it open while these operations have been taking place.)

If there are any problems with your design, the compiler will stop sooner, and error messages will appear in the Message Window below the Main Window in the Quartus screen. Attend to these messages and re-analyse.

If you take a look at the files in your first and first/db folders, you should find that there are now almost fifty files. (You may need to refresh the Explorer window in order to see all the new files, if you have had it open while these operations have been taking place.)

#### Step 6: simulate the design.

This is the stage at which to simulate the design at RTL level. This step allows you check the design logic. You have to devise a set of input signals and then let the software calculate how your design will respond. If the results coincide with the design specification then you start to feel confident that the design will actually work.

As the systems we are looking at are relatively simple, we take the alternative approach of loading the design into the FPGA chip and testing the design on the hardware directly.

#### Step 7: fit your design and download it to the Matrix Multimedia FPGA board

There are actually three stages within this step.

- a. Decide which physical pins on the FPGA chip to use.

- b. Get the Quartus software to 'fit' your design into the FPGA chip.

- c. Download the fitted design to the hardware.

#### Step 7a: adding the pin information

The hardware referred to in these notes comprises the Matrix Multimedia E-blocks FPGA board with a Switch board connected to Port A and an LED board connected to Port B. (Notice that the switch board has to have +5V supplied from the FPGA board by a separate wire.)

With this arrangement, pressing one of the switches generates a logic 1 signal on the corresponding FPGA pin, as shown in the table below. The connections to the LEDs are also given.

| Switch | FPGA pin | FPGA pin | LED |

|--------|----------|----------|-----|

| SW7    | 120      | 84       | D7  |

| SW6    | 119      | 83       | D6  |

| SW5    | 115      | 80       | D5  |

| SW4    | 114      | 77       | D4  |

| SW3    | 113      | 76       | D3  |

| SW2    | 112      | 75       | D2  |

| SW1    |          | 74       | D1  |

| SW0    | 110      | 73       | D0  |

Fig. 4.17.

We use switch SW7 (pin 120) for Input\_A and switch SW5 (pin 115) for Input\_B. For the outputs, we use LED D7 (pin 84) for Output\_A, LED D5 (pin 80) for Output\_B and LED D0 (pin 73) for signal Output\_Q.

To make these pin assignments, first click the 'Pin Planner' icon (or ASSIGNMENTS/PIN PLANNER....)

Double click in the first row of the 'Location' column (for Input\_A.) Enter the number '120'. The software completes the entry as 'PIN\_120'. Click ENTER on the keyboard.

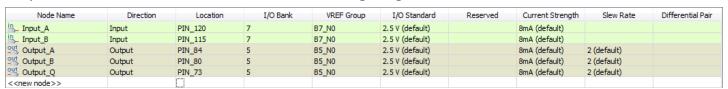

Go down the 'Location' column, adding the pin numbers given above for the other input and outputs. The 'Pin Planner' looks like the following diagram.

Fig. 4.18: Pins assignment.

Close the Pin Planner.

When asked, click to save the file.

Verify that the pin information has been added to the schematic.

#### Step7b: Fit

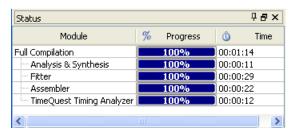

Fitting is part of the compilation process. To start this, click on PROCESSING/START COMPILATION.... The progress of the various stages of compilation is shown in the 'Status' window.

#### Fig. 4.19: Complete compilation

Hopefully, the message 'Full Compilation was successful' will appear after some seconds of activity.

#### Step 7c: Download

You are now at the stage where you have a design file (first\_proj\_top.sof) ready to send to the target board.

In order to do so, the USB Blaster driver must be installed on your computer. Connect the USB cable from your computer to the Matrix Multimedia FPGA board via the USB Blaster.

Apply power to the board using the mains power supply provided, with the voltage set to 7.5V.

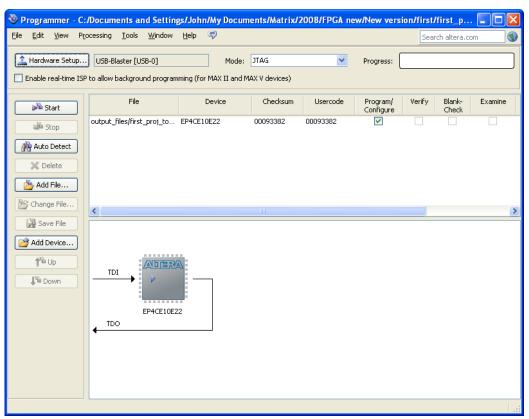

Now click the Programmer button (or select TOOLS/PROGRAMMER ...). The Programmer window should open. Tick the check boxes so that you end up with a window similar to that below.

Fig. 4.20: Programmer ready to download.

Now hit the button, (or select START). The Progress bar should fill, and eventually show 100% completed.

#### Step 8: test the design

The moment of truth - verify that the FPGA chip behaves as a two-input AND gate! Pressing switch SW7 should make LED D7 light up, switch SW5 should light LED D5, and pressing both switches together should make LED D0 light up as well.

#### Note:

The design is still volatile. If you remove power from the FPGA board, your design is lost. A later section shows how to program the design permanently into the FPGA.

# Optional step: Amend the design, re-compile and download

Getting your first design compiled, downloaded, and running on the target hardware takes some effort, but now you should be able to alter the design very easily.

If you have closed down Quartus, you need to launch it again, open the first\_proj project then, if necessary, open the first\_proj\_top.bdf file. Select the AND gate and delete it. Now repeat Step 4 shown earlier, but select an OR gate ('or2') from the 'libraries/primitives/logic' folder and place it in the drawing to occupy the space left by the deleted AND gate. Save the BDF file, and re-compile it.

Now run the programmer again, for the now modified first proj top.sof file.

Verify that you have an OR gate by watching the LEDs on the target board as you press S7 and S5 - either (or both) should cause LED D0 to light up.

Try replacing the gate in your existing design with a NAND gate (nand2 in the 'libraries/primitives/logic' folder.) Save the design file, run a full compilation, use the programmer tool to download the design. Then verify the NAND gate action - the only way to turn off LED D0 is to press both S7 and S5.

# **Permanent transfer**

The programmer will download the first\_proj\_top.sof file to the FPGA hardware, allowing it to be tested, but does not install the code permanently.

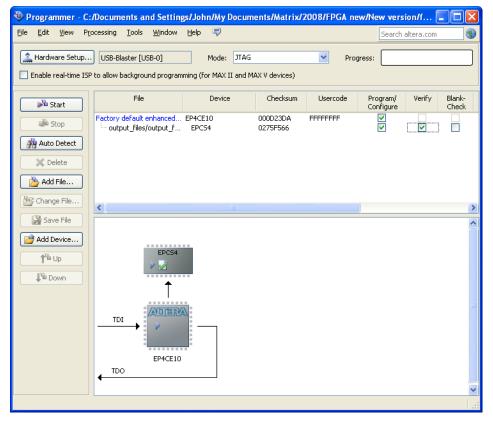

To do so, the file must be converted to a different format, 'JTAG indirect configuration file' (.jic) format.

On the main Quartus screen, click on FILE/CONVERT PROGRAMMING FILES....

In the dialogue box that opens:

- select 'JTAG Indirect Configuration File' (.jic) from the 'Output programming file' type list;

- set the configuration device to 'EPCS4';

- set the mode to 'Active Serial';

- click on 'Flash Loader' and then click on the 'Add Device...' button;

- select the 'Cyclone IV E' device family and then select 'EP4CE10' from the 'Device name' list;

- click on 'SOF data' and then click the 'Add File...' button;

The 'Select Input File' dialogue box opens.

- Navigate to the first\_proj\_top.sof file, in the output\_files folder, select it and click on OPEN.

- The dialogue box now resembles the one shown below

Click the GENERATE button.

The file output file.jic has been created in the output\_files folder.

Next launch the programmer, by clicking on TOOLS/PROGRAMMER. If necessary, add the output file.jic to the programmer. Check the 'Program/Configure' and 'Verify' boxes.

The dialogue box resembles the one shown below:

Click on START to transfer the file to the FPGA hardware.

Once the transfer is complete, press the RESET button on the FPGA board. The program is now written into the FPGA. When you disconnect the board from the computer, the program

still runs on the board. If you disconnect the power supply, and re-attach it, the program is retained, and will still run.

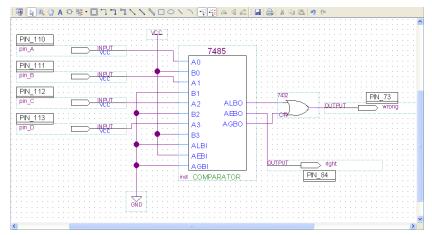

# A second design - the PIN checker

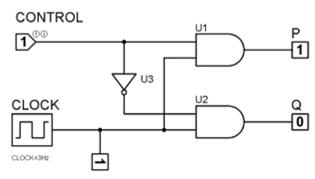

The AND gate example served to identify the processes involved in creating a FPGA design. You can now practice those skills on a more complicated schematic design. The aim:

- a security system requires the user to enter the correct PIN (personal identification number,) in order to be able to use a device;

- the PIN takes the form of a single 4-bit binary number, entered on four switches;

- an LED lights if the PIN is correct;

- a different LED lights if the PIN is wrong.

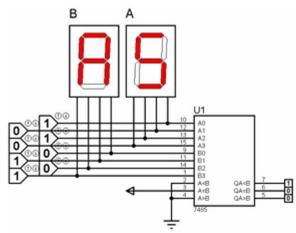

The design shows how two standard logic ICs, the 7485 magnitude comparator and the 7432 quad 2-input OR gate can be mimicked by the FPGA.

The Quartus code to do so is found by adding symbols for the 7485 and 7432 by scrolling down the 'altera/13.0sp1/quartus/libraries/others/maxplus2' library. The 'VCC' and 'GND' symbols (for +5V and 0V respectively,) are found in the 'altera/13.0sp1/quartus/libraries/primitives/other' library.

The 7485 can be cascaded to create an 8-bit comparator, by using the ALBI, AEBI and AGBI inputs (meaning 'A less than B', 'A equal to B' and 'A greater than B' respectively.) As we are not using it in this mode, we need to supply appropriate signals to these inputs, i.e. 0V to ALBI and AGBI, and +5V to AEBI.

We have inserted the correct PIN, as `1001' by connecting inputs B3 and B0 to +5V, and inputsB2 and B1 to 0V.

Assuming that the QuartusII program is already running, work through the sequence that follows.

- Use the New Project Wizard to create a project called PIN\_check, in the directory .../PINcheck, with a top-level file called PIN\_check\_top.

- Assign the design to the correct FPGA device the EP4CE10E22C8.

- Create a new Block Diagram/Schematic file, and save it as PIN\_check\_top.

- Add components, and configure them, to produce the design shown below:

- Start the compilation process by running 'Analysis and Elaboration'.

- Then use the Pin Planner to allocate the FPGA pins shown in the diagram. This uses switches SW0, SW1, SW2 and SW3 to input the PIN ABCD, and shows the result on LEDs D0 (wrong) or D7 (right.)

- Once compilation is completed successfully, run the Programmer to download the design to the FPGA.

- Test it by trying different PINs entered on the switches.

- Further work:

- go back and change the correct PIN in the design, and retest it;

- modify it to use an 8-bit PIN. (You need to add a second 7485, and connect its ALBI, AEBI and AGBI inputs directly to the first 7485's ALBO, AEBO and AGBO outputs.

Connect the OR gate to the outputs of the second 7485 in the same way as above.)

#### **Summary so far**

This exercise introduced you to the Quartus software for developing designs for FPGA devices.

You have seen how to:

- run Quartus;

- set up a project;

- enter a schematic design;

- compile the design;

- download the design to the Matrix Multimedia FPGA target board.

In the next section, you enter the design using the Verilog hardware description language, rather than by using a schematic diagram.

# **Chapter 5: Advanced Quartus II features**

### Introduction

In this section, we introduce further projects and exercises. It is designed to teach you the capabilities of Quartus, and project management within Quartus, rather than digital electronics design. You may want to come back to this section later, when you are developing more advanced projects.

The discussion in this section focuses only on the use of Block Diagram Files. However, Verilog or VHDL files can be incorporated easily into the design philosophy described here. If your projects are relatively simple, you may want to skip this chapter and continue to chapter 6, which concerns the design of FPGA programs using Verilog and VHDL.

# Introduction

In this section you learn:

- how to compile a traffic light design from basic design elements;

- how to design all the elements from scratch.

- We have split this section into two parts:

- the first part looks at how all the parts of Quartus work. For this section, we provide all the design elements. You need to put them in the right place and enter the correct information within Quartus, to 'glue' the design together.

- the second part concentrates on entering an actual circuit. (If you get stuck, you should refer to the design files in part one.)

#### Putting a project together

One of the more difficult aspects of learning how to use Quartus, is understanding the structure of a project, and the settings that are required.

Here, we concentrate on putting a project together from all its elements. In the next section, we look at how to construct the elements themselves.

We will put together a traffic light controller that consists of three circuit blocks:

- a two bit counter (a four-state machine);

- a combinational circuit to decode the red, amber and green signals;

- a top level circuit block that ties these together.

As you have seen, a simplified design flow of a project is as follows:

- design your circuit;

- compile your design;

- design your simulation;

- simulate your design;

- program your FPGA.

Of course, this will rarely be as linear. You usually need to reiterate this process, and modify your design, before the design is right.

This section aims to help you to understand this design flow, and the hierarchical nature of Quartus. Pay special attention to getting the compilation and simulation settings right as that is usually where problems start.

# **Hardware settings**

We will use the same E-blocks configuration described earlier:

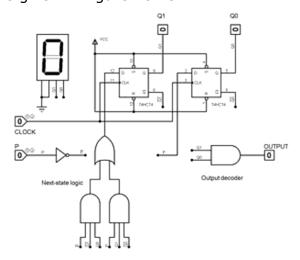

Fig. 4.1: E-blocks layout.

The 7-segment display is on Ports C and D, the switch board is on Port A, the LED board on Port B and the keypad board is on Port E.

### **Instructions**

To do this:

- Make a new directory called 'empty\_traffic'.

(If you have the Matrix CD ROM you may find this directory exists already.)

- 2. Copy the following files to this directory:

```

Traffic.bdf;

Combinationalpart.bdf;

2 bit counter.bdf;

```

(Ask your supervisor for copies of these files if you do not have them.)

- 3. Open Quartus and select FILE...NEW PROJECT WIZARD. Select the name of the project and the top level entity as 'traffic'

- 4. NEXT

- 5. Select the three BDF files: ADD ALL, NEXT

- 6. Set the Family to 'Cyclone 4E', and select the chip 'EP4CE10E22C8', and then click on

#### **FINISH**

- 7. Next, examine the three \*.bdf files. To do this open the Project Manager window and select the FILES tab. You should be able to see these three files. Open each one in turn, by clicking on it, and look at the overall circuit. Hopefully you will recognize that the design of this circuit consists of two low level circuit blocks ( combinational-part.bdf , and 2\_bit\_counter.bdf ) and a high level circuit that is comprised of these two low level circuits.

- 8. Compile your design by selecting PROCESSING...START COMPILATION.

You have now compiled a complete project. (You may decide to practise this exercise again to become familiar with the design flow.)

If you want to you can assign pins and send the program to the development board. However, for it to work, it needs a clock signal. This will be addressed in the next section.

# A new task

Now, you have a better understanding of how the various design elements combine to make up a Quartus project file. We repeat the exercise but design all the individual elements of the project, to show you how to enter designs.

Here you will learn:

- how to design a sequential logic circuit;

- how to simulate and test this circuit;

- how to configure Quartus to make a more complex project.

We recommend that you work carefully through this section to ensure that you are familiar with the settings in Quartus. Remember to follow the text carefully to avoid mistakes. This may seem laborious – but it is worth doing!

### **New brief**

A traffic light controller consists (in its simplest form) of a two stage counter and some combinational logic to decode the status of the red, green and amber lights. (Notice that we are basing the design on the British traffic light system. If you are not in the UK, then you can vary this design to mirror your own national system later.)

Our aim is to teach you how to use Quartus. We assume that you are already aware of how traffic lights work. If not, then please refer to our Digital Electronics CD ROM where this design is explained further.

We are going to split this design into two stages:

- first, we design the circuit elements a simple two bit counter and some combinational logic;

- once these are working, we design a higher level block that ties the two together as a complete circuit.

This is not the cleanest way of designing a circuit! Really, we should start with blocks, declare the inputs and outputs to the blocks and then design the blocks themselves.

like:

However this technique is one that needs practising!

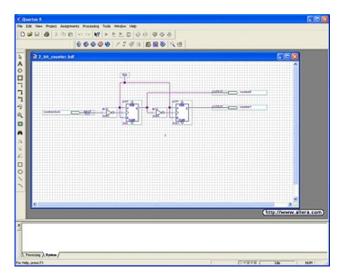

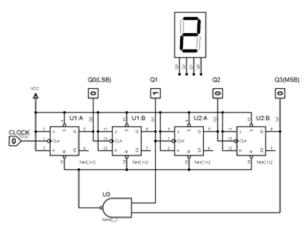

# **Building the two bit counter**

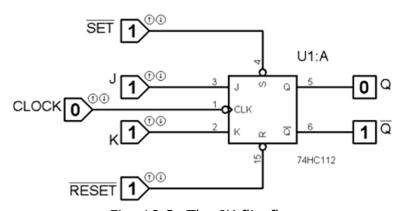

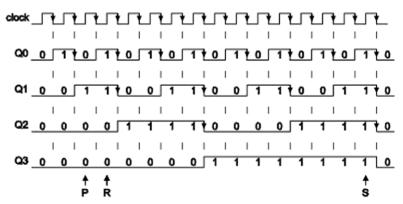

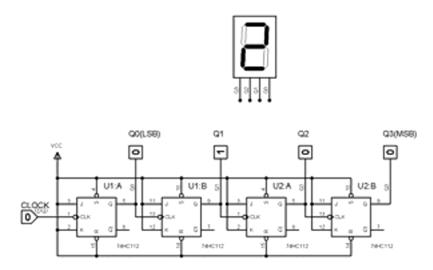

Our traffic light design consists of a two-bit counter made from JK flip flops. To keep the design neat, we will separate the counter components from the combinational logic components.

To build the counter section, follow these instructions:

1. Start Quartus and set up a new project - traffic.quartus.

2. Start a new Block Diagram File and design a two-bit counter. Use JK flip flops from the storage symbol section. Call the input counterclock, and the two outputs counter0 and counter1. Save the design as 2\_bit\_counter.bdf. You should have a

design that looks

Fig. 5.1: 2 bit counter.

- 3. For this project, we build the combinational logic separately from the counter circuit. We could get the whole circuit in one Block Diagram File but it is good practice to break the design into separate elements. When doing so, we need to specify the hierarchy of each element just as you would in a software program, where you define functions and sub routines. You need to let Quartus know where the file 2\_bit\_counter.bdf sits in the hierarchy of your design, for the compiler. To do this, select PROJECT....SET as TOP LEVEL ENTITY.

- 4. Make sure your design compiles, by selecting: PROCESSING...START COMPILATION. (You will not be able to find the nodes of your design unless you compile first.)

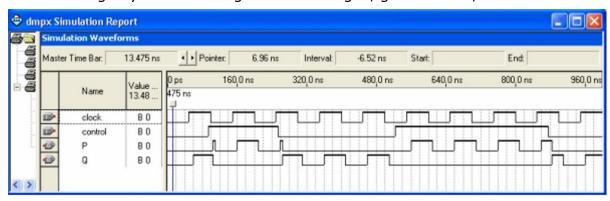

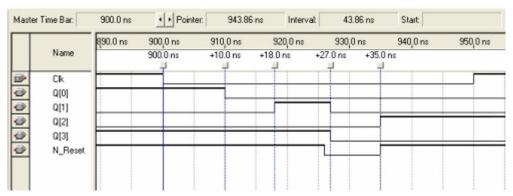

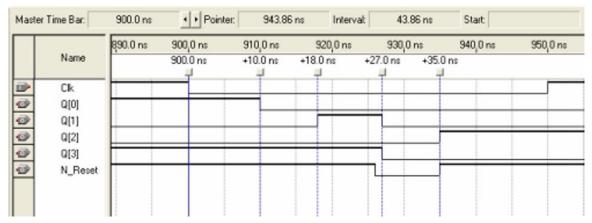

### **Testing the two bit counter**

This section shows you how to simulate the two-bit counter.

Build a Vector Test Waveform that clocks the input at regular intervals. Make sure that the two outputs count upwards. Save this as 2 bit counter.vwf.

| County | See | County | Coun

You should have something that looks like:

Fig. 5.2: Testing the counter.

You can use this to test the two-bit counter.

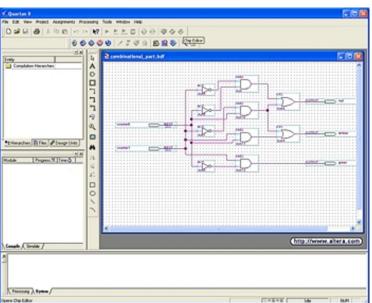

# **Building the combinational sections**

Next, we move on to design the combinational logic part of the circuit. To do this:

1. Make a new Block diagram file with inputs labelled counter0 and counter1 and outputs red, amber and green. The following screen image shows how to connect them:

Fig. 5.3: Building the sections.

Set the compiler focus on to this object to add it to the

hierarchy. To do so, select PROJECT....SET AS TOP LEVEL ENTITY.

3. Compile this part of the design

# Creating a top level design

We are going to create sections that Quartus can recognize, for each of the two circuits we have designed. We can then design a top level design circuit that refers to each of these new parts. In practice, we will be creating two new symbols - one for the 2-bit counter and one for the combinational logic block.

#### To do this:

- 1. Open the 2-bit counter.

- 2. From the FILE menu select CREATE/UPDATE....SYMBOL FILE FROM CURRENT FILE. Quartus will create a new project symbol from the 2-bit counter file. You can check this by clicking on the Symbol tool, expanding the project library by clicking on the '+' next to 'Project' and you will see your new symbol listed there.

- 3. Repeat this for the combinational logic circuit.

Now we can create the top level design.

#### To do this:

- 1. Create a new BDF and save it as traffic.bdf.

- 2. Click on the symbol tool and expand the Project library. Place a '2\_bit\_counter' symbol and a 'combinational part' symbol.

- 3. Insert an input clock and output pins.

- 4. SAVE the file.

- 5. Select PROJECT...SET AS TOP LEVEL ENTITY

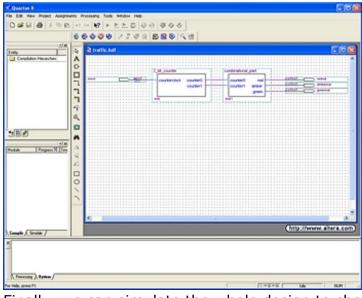

# You should end up with:

Fig. 5.4: Top level design.

The next step is to compile this design to check for errors.

# Simulating the whole project

Finally, we can simulate the whole design to check it all works.

### To do this:

- 1. Select FILE ...NEW... OTHER FILES....VECTOR WAVEFORM FILES.

- 2. You should know how to set up the waveform file refer to earlier sections if in doubt!

- 3. Save as traffic.vwf.

- 4. Update the Assignments setting for this simulation.

- 5. Simulate your file.

Open the Project Navigator screen. You can see that this project consists of:

```

Device design files

Traffic.bdf

Combinationalpart.bdf

2_bit_counter.bdf

Software files

none

Other files

2_bit_counter.vwf

traffic.vwf

```

#### **Exercises**

#### **Exercise 1**

Load the traffic project into Quartus. Make sure you can compile and simulate it. Look at this project in detail to reinforce your understanding of Quartus.

#### **Exercise 2**

Build this project again from scratch, to make sure that you understand all the elements of Quartus. (If necessary, refer to earlier instructions.)

#### **Exercise 3**

As you can see, there are some errors in the combinational logic part of the design which result in the traffic light output sequence being incorrect.

Redesign the circuit so that the sequence is as follows:

- Green

- Amber

- Red

- · Red and amber

- Green

- etc....

#### **Exercise 4**

The traffic light combinational logic circuit is quite inefficient as it uses more gates than are necessary. Redesign the it to use fewer gates. Verify that the circuit works using simulation.

### **Exercise 5**

In practice, a crossroads could consist of four sets of traffic lights, running two different cycles of lights.

Assuming that they are generated by a simple 4-stage state machine (like the original design,) make a table that shows the output sequences.

Then design a circuit that produces the following sequence of outputs:

| Counter0 | Counter1 | Red 1 | Amber 1 | Green 1 | Red 2 | Amber 2 | Green 2 |

|----------|----------|-------|---------|---------|-------|---------|---------|

| 0        | 0        | off   | off     | on      | on    | off     | off     |

| 1        | 0        | off   | on      | off     | on    | on      | off     |

| 0        | 1        | on    | off     | off     | off   | off     | on      |

| 1        | 1        | on    | on      | off     | on    | off     | off     |

Prove your design through simulation.

#### Exercise 6

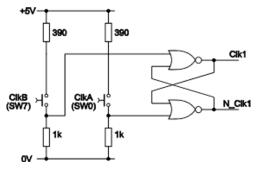

Assuming that the board is supplied with a 20MHz clock, create a suitable circuit to divide the clock frequency down to 1 Hz and use this as a clock source for the two-bit counter. Take this design one stage further by assigning pins for the hardware and downloading the design into the FPGA.

### **Introduction to 'top-down'**

In the previous section, we looked at building Quartus projects 'bottom-up', starting from individual design elements, assigning symbols for each of these and then tying the whole design together in a top level design.

In this section, we examine the other approach – 'top-down'. In this, we start by creating the topology of the design and then develop circuitry for each of the blocks in it.

This section does not contain step-by step instructions for the project. If you find progress difficult, then go back to previous sections and practise your design building there first.

It is recommended that, in addition, you take a look at Altera's own tutorial 'My First FPGA Design', which offers a very good overview of the 'top-down' approach. (This is available to download from the Altera website.)

#### Top down approach

In this section, we examine:

- the top down approach to logic design;

- how Quartus assists the design of more complex projects;

- how to incorporate 74xxx elements into your design.

This project starts to demonstrate the real benefits of FPGAs. For projects consisting of only a few flip-flops and some discrete logic, the benefits of FPGAs are slim. They come into their own when projects become larger and more complex. This project will give you an appreciation of how and why.

From now on, we assume that you have got to grips with the Quartus interface and the way Quartus works. We no longer take you through menus step-by-step. Instead, we concentrate on explaining the systems in place.

#### A counter design

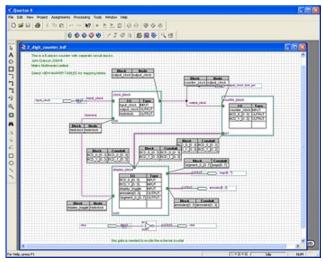

Load the project file two digit counter.quartus.

This is quite a large project, which compiles into 44 macrocells. It is structured in a way that allows for easy design generation and updating.

Make sure the Project Navigator window is open, and explore the elements in the project. The top level entity is two digit counter.bdf which looks like:

Fig. 5.6: Counter design.

#### Notice that:

- The whole project is contained under the BDF file 2\_digit\_counter.bdf .

- In 2\_digit\_counter.bdf, you can see that the project consists of three sub elements: display\_block, counter\_block, and clock\_block.

- In the 2\_digit\_counter.bdf file, we have used the shorthand wiring notation `[0..7]' to allow us to wire buses together easily.

- This shorthand notation can also be used for input and output pins to avoid cluttering up your designs.

- When wiring blocks together with conduits, you need to specify the bus lines in the conduit and how these connect to the block elements at each end of the conduit.

- The easiest way to access any part of the design is to double click on each block to reveal the sub circuit it represents.

- This block approach allows newcomers to the design to see how the design works.

- Where a conduit enters a block, there is a small green symbol. Right mouse clicking on this block allows you to map the conduit connections to the block connections.

- There is an option to allow you to view/hide conduits. Check your VIEW menu if you are having trouble here.

- The naming of all conduits and signals is meaningful to aid understanding

- The pin assignment editor knows when you have used an input and output bus and puts pin connections on automatically to aid debugging

- In display block, and counter block we have used standard 74xxx parts.

- Where you come across a 74xxx part, you can double click on it in the Project Manager

window to see its elemental form. These are 'off the shelf' parts supplied by Altera and can be found in the OTHERS... section of the symbol library.

The disadvantage of using 74xxx components is that relating the datasheet to the symbol can be tricky.

#### Top down design

The 'top-down' design method is important for several reasons:

- it encourages you structure the design in sections;

- it allows a number of designers to work on a project at the same time, each being responsible for one of the sections of the design;

- it is easier to debug;

- it facilitates development in manageable 'chunks', likely to be reusable in future designs;

- it is easier to document.

# What's in the design so far?

The design files consist of:

- Device design files

- Counter\_block.bdf

- 2\_digit\_counter.bdf

- clock\_block.bdf

- display\_block.bdf

- \..\..~\7447.bdf

- \..\..~\7490.bdf

- Software files

- none

# Fill in the blanks

The project in the directory `Partial\_Two\_Digit\_Counter on the CD ROM is a variation of the 2\_digit\_counter project that has had the clock block removed.

#### You need to:

- copy this directory to an appropriate place on your C: drive;

- create a new block to replace the clock circuitry;

- edit the top level block design file ( Two\_digit\_counter.bdf ) to include this new file;

- add output pins for the dual 7-segment display;

- recompile the design;

- verify (through simulation or otherwise) that the design works.

- There are several ways in which you can replace the clock circuit:

- you can design a clock circuit using individual flip-flops;

- you could use a 74 series counter;

- you could try using VHDL, (if you were feeling ambitious).

Note - you can copy the file clock\_block.bdf from the original Two\_bit\_counter directory if you want to save time!

You should practice creating the clock block.bdf from the block symbol if possible.

# **Light-chaser - Megafunctions**

Megafunctions are modules, designed by Altera for use in FPGA designs. They are installed by default in the QuartusII suite, in the 'libraries/megafunctions' folder, when you down load the Quartus II software. Their function is to save the user time and effort when creating a FPGA design.

We will access them using the 'MegaWizard Plug-in Manager'.

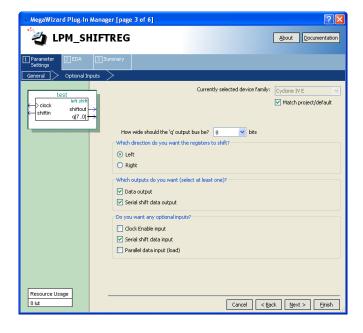

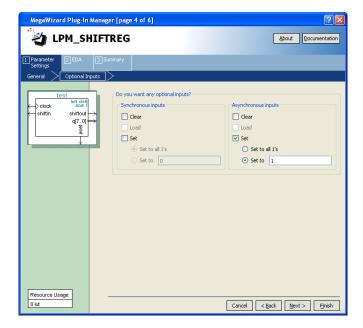

The task is to design a light-chaser, where one LED is lit, and then a short time later, the LED to its left is lit, and so on. This behaviour repeats over and over again.

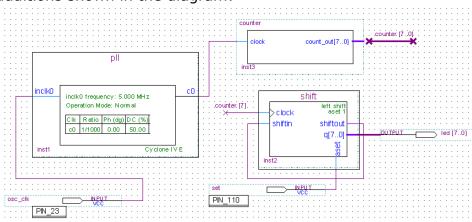

The design requires a clock signal to make the light-chaser pattern move to the next stage. We will use a phase-locked loop (PLL), configured by the 'MegaWizard Plug-in Manager'. The clock frequency from this will be too high, so we follow it with a counter, whose role is simply to generate a lower frequency clock signal.

It is followed by a shift register. In this, the stored data moves one position to the left on each clock pulse. Its outputs will be connected to the LEDs, and will show the light-chaser effect.

Assuming that the QuartusII program is already running, start the new design as follows.

- Use the New Project Wizard to create a project called chaser, in the directory .../chaser, with a top-level file called chaser\_top.

- Assign the design to the correct FPGA device the EP4CE10E22C8.

- Create a new Block Diagram/Schematic file, and save it as chaser\_top.

# <u>Light-chaser - Using the Megafunctions PLL</u>

You just created the chaser\_top.bdf file. The task now is to add the components described in the previous section.

First, the phase-locked loop:

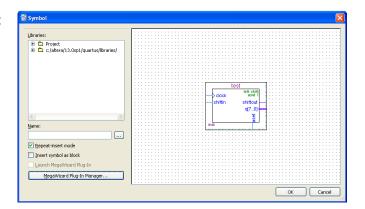

• Click on the 'Symbol' icon and then on the 'MegaWizard Plug-in Manager...' button. The first page of the wizard appears.

The action to create a new megafunction is already selected, so click NEXT.

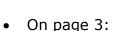

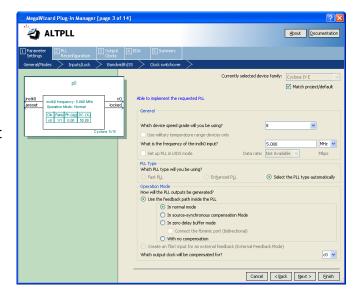

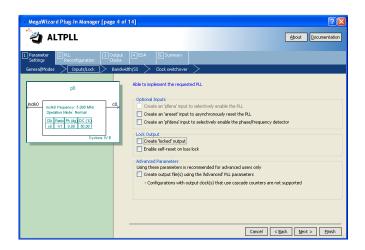

# On page 2a of the wizard:

- expand the 'I/O' folder by clicking on the '+' next to it;

- select the megafunction called 'ALTPLL';

- check that the 'Cyclone IV E' family is chosen;

- select 'Verilog HDL' as the output file type;

- name the output file by adding pll on the end of the directory name given;

- click NEXT.

- confirm that the `Currently selected device family' is still Cyclone IV E;

- leave the selected speed grade as '8';

- change the frequency of the 'inclk0' input to 5 MHz;

- leave 'PLL type' and 'Operation mode' at their default settings;

- click NEXT.

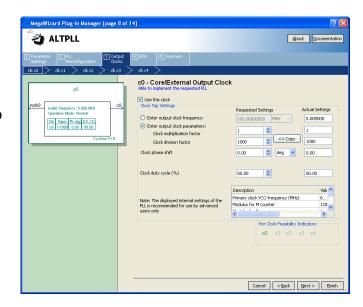

- On page 4:

- uncheck all options;

- click NEXT, and then click tab 3 'Output Clocks', which takes you to page 8.

- On page 8:

- change the 'clock division factor' to 1000;

- leave all other settings unchanged;

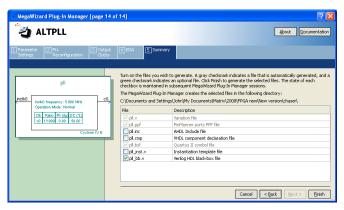

- click FINISH, (as the remaining pages do not require attention.

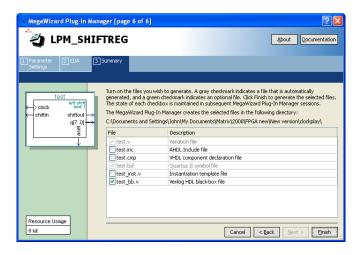

- The wizard displays a summary of the files it has created:

- click FINISH again.

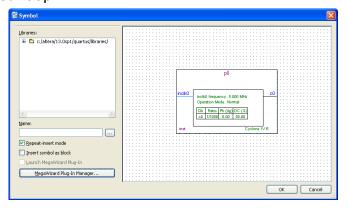

Quartus generates a symbol for the phase-locked loop:

- click OK;

- drag an image of the symbol onto the main workspace, and click again to release it;

- press escape to prevent any further instances of the image.

# <u>Light-chaser - Verilog counter</u>

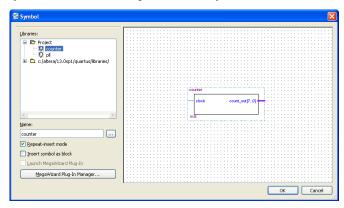

The output clock frequency from the phase-locked loop is too high for our purposes. We are going to follow it with an 8-bit counter, purely to lower that frequency.

The method chosen is to write the code for the counter in Verilog. (VHDL could have been used equally well.)

53

#### To do this:

- create a new file, and choose a Verilog HDL Design File, (FILE / NEW / VERILOG HDL..);

- save it as counter.v; (FILE / Save As...) and then click SAVE;

- type the following code into the main workspace for the Verilog file:

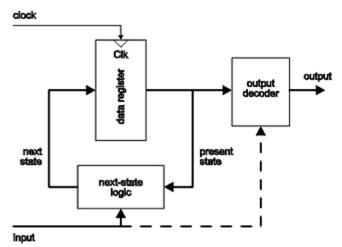

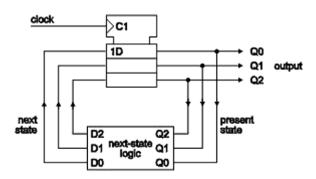

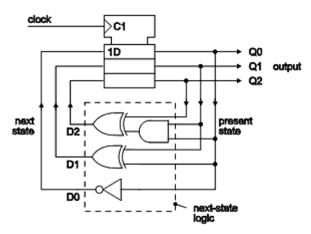

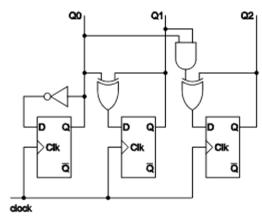

- save the Verilog file, (FILE / SAVE);